数十年来,在摩尔定律推动下,半导体行业一派向好。

随着工艺制程不停生长,台积电、三星、英特尔等晶圆代工厂商之间的竞争已进入先进制程赛道。在此历程中,EUV极紫外光刻装备成为各厂商争取的焦点。

据报道,2024-2025年,台积电将接受60台EUV光刻机,预估总用度将超122亿美元;英特尔率先拥抱全球*台High NA EUV光刻机;三星也在向High NA EUV光刻机跃跃欲试,试图追赶台积电。

EUV光刻机遭争抢背后,各晶圆大厂同样有魔难言。其中,高昂的光刻机用度,对半导体厂商而言无疑就是一种伟大的肩负。

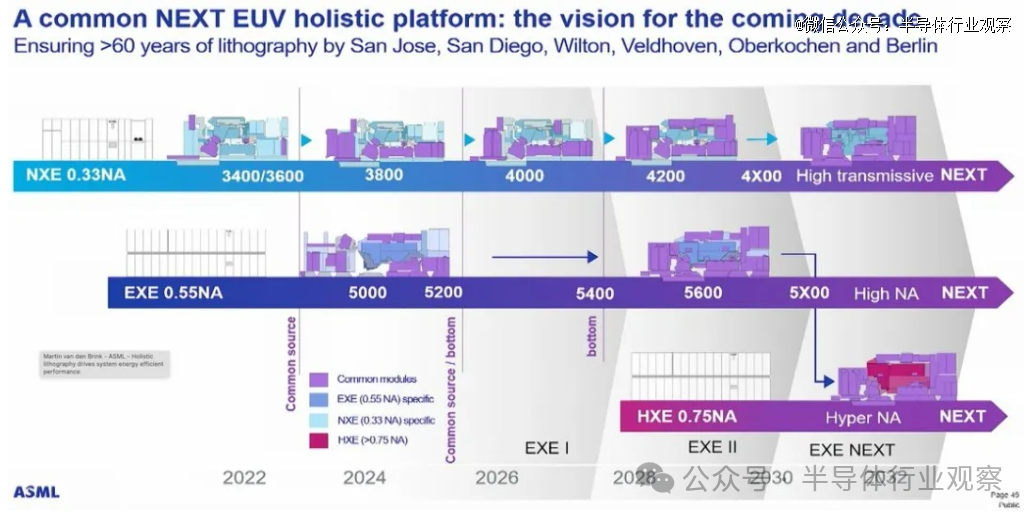

据悉,现在0.33NA EUV光刻机的售价约为1.81亿美元每台,新一代的High-NA(0.55NA) EUV倍增至2.9-3.62亿美元一台。而进入1纳米以下的埃米世代后,ASML将设计推出更先进Hyper-NA(0.75NA)EUV光刻机装备,其售价则有可能跨越7.24亿美元。

ASML光刻机蹊径图

在此价钱压力下,一度让台积电、三星、英特尔等半导体晶圆代工厂商望而却步。

例如2023年英特尔代工营业亏损70亿美元,其接纳下一代EUV光刻机而造成成本肩负即是缘故原由之一;台积电也曾多次指出下一代EUV装备价钱太贵,甚至示意A16先进制程节点并纷歧定需要High NA EUV;而困于良率瓶颈的三星,在云云高昂的装备成本眼前同样十分挣扎,在其SF1.4节点的宣传中甚至都未提到High NA。

可见,装备成本问题已成为各先进制程代工厂设计未来工艺时的主要思量因素。

在此靠山下,“降本”与“替换”成为摆在EUV光刻机眼前的两个选择。

EUV光刻降本,多路出击

FEL,替换EUV-LPP光源

EUV光刻机之以是云云昂贵,其中一个要害缘故原由在于EUV光源的生产,接纳的是现在地球上最壮大的商用激光器,通过轰击金属锡滴来发生13.5nm EUV光源。

ASML当前所接纳的激光等离子体EUV光源(EUV-LPP)光源价钱昂贵,效率低下,光电转化率仅为3%-5%。

对此,一个非通例的替换方案正在酝酿中。日本高能加速器研究组织(KEK)的研究职员以为,若是行使粒子加速器的气力,EUV光源的获取可能会更廉价、更快、更高效。

现实上很早就有研究职员就看到了使用由粒子加速器发生的称为自由电子激光器(FEL)来发生壮大的EUV光源的可能性。

FEL行使电子在磁场中的运动发生*激光,其效率比通俗EUV光源凌驾一倍,能量转化率跨越30%,且拥有成本低、功率大等优势。在电力消耗方面,FEL光源也要远低于EUV-LPP光源。

KEK高级光源研究员示意:“EUV-FEL光束的极高功率、窄光谱宽度和其他特征使其适互助为未来光刻的EUV光源来应用。”

此外,EUV-FEL还可升级为BEUV-FEL,以使用更短的波长(6.6-6.7 nm)实现更细腻的图案化。它还可以可变地控制FEL光的偏振,以实现High NA光刻。

据悉,现在业界已经设计了一种基于能量接纳直线加速器(ERL)的FEL光源用于未来的光刻,而且已经研究和开发了主要组件。FEL光源在EUV功率、升级到BEUV-FEL、High NA光刻的偏振控制、电力消耗和每台光刻机的成本方面具有许多优势。

EUV-FEL光源被以为是未来光刻最有前途的光源,应进一步推动其产业化。

应用质料,EUV图案化的一场革命

为了辅助芯片制造商继续缩小设计,同时又不增添EUV双重图案化的成本、庞大性以及能源和质料消耗,应用质料与*客户亲热互助,在去年开发了Centura Sculpta图案化系统。

基于此,芯片制造商可以打印单个EUV图案,然后使用Sculpta系统在任何选定的偏向上拉长形状,以削减特征之间的空间并增添图案密度。由于最终图案是由单个掩模确立的,因此降低了设计成本和庞大性,并消除了双图案对齐误差的良率风险。

简朴来说就是,原本需要两次EUV曝光才气完成的历程,现在借助应用质料公司的 Centura Sculpta图案化系统,就只需要一次EUV曝光就能完成。

与此同时,EUV双重图案化需要许多分外的制造工艺步骤,通常包罗CVD图案化薄膜沉积,CMP清洁,光刻胶沉积和去除,EUV光刻,电子束计量,图案化薄膜蚀刻和晶圆清洁等。

对于其所取代的每个EUV双图案序列,Sculpta系统可以为芯片制造商提供:

每月生产能力每10万片晶圆可节约约2.5亿美元的资源成本

每片晶圆可节约约50美元的制造成本

每片晶圆节能跨越15千瓦时

每片晶圆可直接削减0.35千克二氧化碳当量以上的温室气体排放

每片晶圆节水约15升

应用质料资深副总裁暨半导体产物事业群总司理Prabu Raja示意,新的Sculpta系统充实证实晰质料工程的提高,可以补强EUV光刻手艺,协助芯片制造商*化芯片面积和成本,并解决先进芯片制程日益增添的经济和环境挑战。Sculpta系统怪异的图案成形手艺,连系了应用质料公司在带状离子束和质料移除手艺方面的深挚专业知识,为图案化工程师提供了突破性的创新工具。

TechInsights副主席Dan Hutcheson示意,应用质料公司的新Sculpta系统是图案化的一场革命,为芯片制造商带来了全新的功效。随着行业不停突破芯片扩展的极限,我们需要像应用质料公司的图案成形手艺这样的突破,以提高芯片功耗、性能、面积和成本,同时降低设计成本、能源和质料消耗。

Sculpta是自引入CMP以来晶圆制造中*创新性的新工艺步骤,受到*芯片制造商的高度关注,并被选为大批量逻辑制造中多个步骤的纪录生产工具。

在今年2月,应用质料又新推出了一款新的电子束丈量装备,专门用于准确丈量接纳EUV和新兴的High-NA EUV光刻手艺的半导体器件的要害尺寸,可有用降低光刻工艺的成本。

据悉,该装备被称为VeritySEM 10要害尺寸扫描电子显微镜(CD-SEM)丈量系统。

据应用质料公司称,与传统CD-SEM相比,该装备能够以较低能量实现2倍分辨率,并提升30%的扫描速率。该装备*的分辨率和扫描速率改善了对EUV和High-NA EUV光刻和蚀刻工艺的控制,以辅助芯片制造商加速工艺开发并*限度地提高峻批量制造的产量。

“VeritySEM 10是CD-SEM手艺的一项突破,它解决了未来几年将塑造行业的重大手艺转变带来的计量挑战,”应用质料公司成像和历程控制团体副总裁Keith Wells说,“该系统独专程连系了低着陆能量、高分辨率和更快的成像速率,有助于为High-NA EUV、GAA晶体管和高密度3D NAND铺平蹊径。”

东京电子,应对EUV双重图案化挑战

东京电子推出了Acrevia工具,这是一款新型气体团簇光束 (GCB) 系统,专为细化EUV光刻确立的图案而设计。

该工具接纳低损伤外面处置,可用于多种用途,包罗削减即将推出的节点的EUV多重图案化使用量、增强线边缘粗拙度以降低性能转变、削减随机光刻缺陷,并最终降低芯片制造成本并提高产量。

众所周知,尺度的单次EUV图案化工艺流程包罗八个要害步骤:晶圆沉积、化学机械抛光清洁、光刻、计量、图案蚀刻、清洁、计量和晶圆蚀刻。除了晶圆蚀刻外,所有步骤均重复举行,以举行双重图案化。

然而,双重图案化 EUV 手艺带来了新的挑战,包罗成本增添、良率可能下降以及生产周期延伸。东京电子建议在光刻图案化和随后的干蚀刻步骤之后将其Acrevia工具插入工艺手艺流程中,而不是双重图案化。若是需要,Acrevia工具也可以用于双重甚至三重EUV图案化之后举行改善。

虽然Acrevia工具不会取代双重或三重EUV图案化,但它可以削减其使用量并改善图案,从而提高性能和良率,这意义重大。

此外,由于EUV光刻手艺会发生随机效应,这些效应会导致随机桥接缺陷和较差的线边缘粗拙度等问题。由于这些缺陷具有随机性,因此很难检测到。纵然使用EUV双重图案化,也无法完全消除这些缺陷。东京电子示意,其图案细化工具可以改善图案侧壁的线边缘粗拙度 (LER) 并削减随机光刻缺陷,从而提高良率。

总结来看,Acrevia接纳了东京电子原创手艺,可实现高蚀刻速率和低损伤图案化。在日益具有挑战性的先进图案化领域,Acrevia使进一步扩大规模成为可能,并*限度地提高了生产率。

EUV光刻,替换危急

极紫外光(EUV)光刻手艺是现在*进的光刻手艺,它可用于制造制程小于7nm的芯片,但也面临着手艺难、成本高、工艺庞大、供应链封锁等问题与挑战。

因此,许多研究机构和企业都在探索其他的先进制程手艺,实验挑战ASML在超细腻制程芯片制造装备方面一家独大的职位。

纳米压印手艺(NIL)

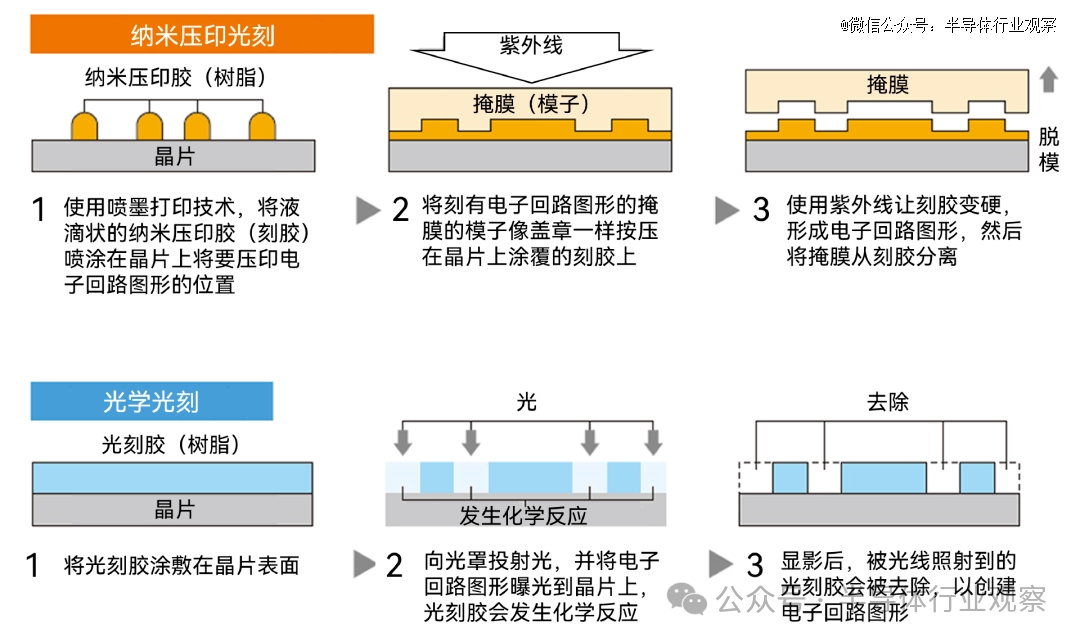

纳米压印(NIL)手艺是将印有电路图案的掩模压印在晶圆外面的抗蚀剂上,通过类似于印章的形式制造集成电路,将掩模上的细腻电路图案转移到晶圆上,可在单个压印件中形成庞大的二维或三维电路图案。

紫外纳米压印光刻与光学光刻流程对比

美妆达人去哪儿了

可以明白为,纳米压印手艺造芯片就像盖章一样,把栅极长度只有几纳米的电路刻在印章(掩膜)上,再将印章盖在橡皮泥(压印胶)上,实现图形转移后,然后通过热或者紫外线光照的方式使转移的图形固化,以完成微纳加工的“镌刻”步骤。

笔者在此前文章中曾写到,与传统的光刻手艺相比,首先,纳米压印手艺不需要庞大的光路系统和昂贵的光源,可以大幅降低制造成本。

另外,纳米压印的模板比光刻机用的掩膜疆土案设计更简朴,压印出来的图案尺寸完全由模板上的图案决议,以是不会受到传统光刻胶手艺中光源波长、光学衍射的限制和影响。与光刻装备发生的图案相比,纳米压印手艺忠实地再现了更高分辨率和更大平均性的图案。

同时,纳米压印手艺只要预先在掩膜上制作好图案,纵然是庞大结构也能一次性形成,同时也阻止了传统光刻工艺中的多次重复曝光,进一步提升了成本优势。据日经中文网报道,纳米压印能省掉成本伟大的光刻工序的一部门,与极紫外光刻相比,能将该工序的制造成本降低4成,耗电量降低9成。

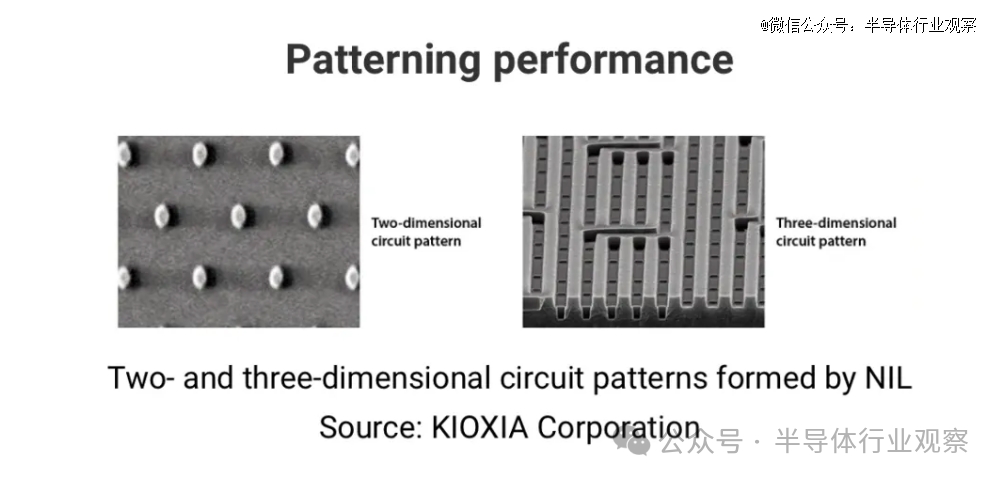

此外,纳米压印手艺在三维立体结构加工方面有着它怪异的优势,传统的光刻手艺都是基于二维平面的加工方式,三维结构获取对照难题,同时可控性较差,然则对于纳米压印手艺,只要制作成模板,就可以批量生产三维产物。

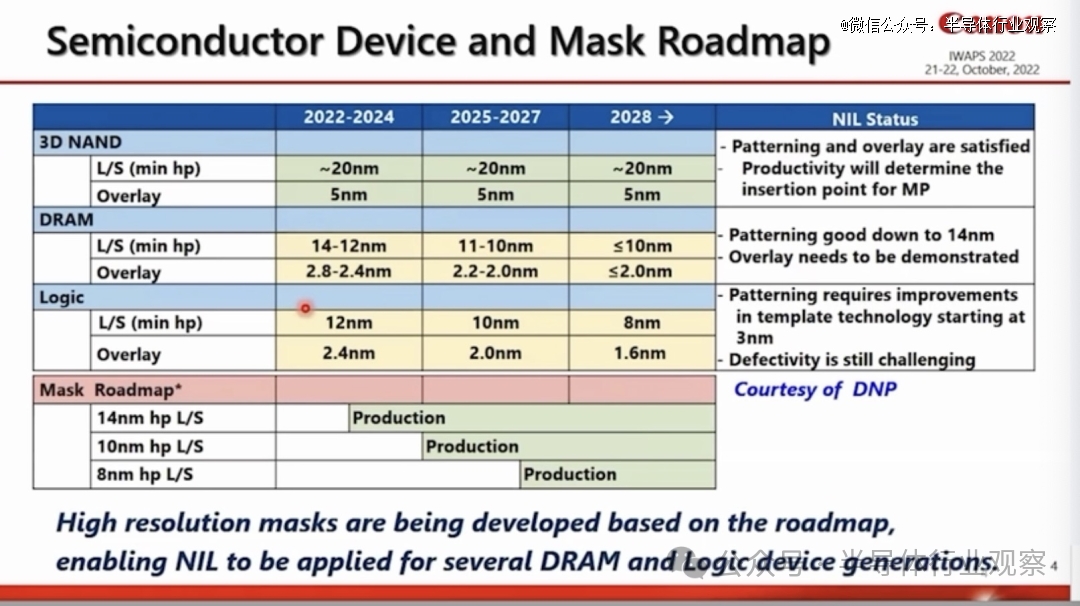

2023年10月,日本佳能公司宣布推出纳米压印芯片制造装备,现在可实现最小线宽为14nm的图案化,约即是5nm工艺节点;未来有望实现最小线宽为10nm的电路图案,相当于2nm工艺节点。现在,日本铠侠公司已经将NIL手艺应用到了15nm NAND闪存器上,并有望在2025年推出接纳NIL手艺的5nm芯片。

克日有新闻披露,SK海力士从佳能引进了纳米压印装备,现在正在举行测试,设计在2025年左右使用该装备最先量产3D NAND闪存,到现在为止的测试效果优越。另一存储巨头三星同样开发了包罗纳米压印手艺在内多种方案以解决多图案工艺导致的成本上升问题。

除了在NAND闪存领域的探索外,佳能还正在实验将NIL手艺应用到DRAM和CPU等逻辑芯片上。

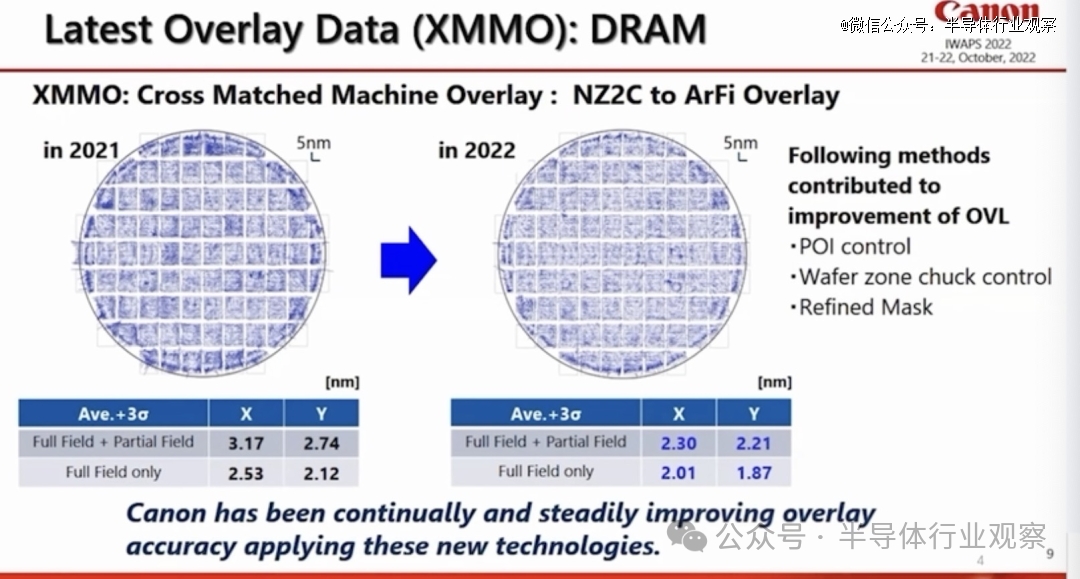

针对DRAM方面,佳能一直在不停改善套刻精度。使用POI 控制手艺、晶圆区卡盘控制、细腻掩膜等方式有助于改善套刻精度。

图源:佳能

高级的NIL工具和掩膜相连系可以为许多差其余应用提供多种解决方案,佳能展示了2.3nm套刻精度应用于种种新手艺,主要用在DRAM方面。

在芯片领域,纳米压印光刻更善于制造3D NAND、DRAM等存储芯片,与微处置器等逻辑电路相比,存储制造商具有严酷的成本限制,且对缺陷要求放宽,纳米压印光刻手艺与之较为契合。

据佳能在纳米压印装备未来蹊径图显示,应用将从3D NAND存储芯片最先,逐渐太过到DRAM,最终实现CPU等逻辑芯片的制造。

图源:佳能

经由近30年的研究,纳米压印手艺已经在许多方面有了新希望,海内外半导体装备制造商、质料商以及工艺商纷纷最先涉足这一领域。

尤其是以佳能为代表的日企,欲通过半导体“纳米压印手艺”来追赶ASML的脚步。

据TechNavio数据显示,2026年纳米压印市场有望到达33亿美元,2021年至2026年年复合增进率可达17.74%,该市场虽然没有想象中那样大,但整体正逐渐走强。

那么,纳米压印手艺能否替换EUV光刻呢?

忠实来讲,难度是异常大的,实在从行业动态也能看到,每隔几年都市有纳米压印光刻即将突破的新闻,但每次又延后进入产业的时间。

现在纳米压印手艺还存在模板缺陷和套准等问题,需要时间才气成熟地进入市场,但其超高分辨率、易量产、低成本、一致性高等优点已经很突出,是最有时机取代现有光刻手艺的手艺手段之一。在未来光学光刻难以向前演进时,纳米压印手艺或将是一条值得期待的光刻蹊径。

定向自组装光刻(DSA)

定向自组装光刻(DSA)是一种行使质料自身的分子排列纪律,诱导光刻质料在硅片上自觉组成需要的图案的方式,它比传统光刻分辨率更高,加工速率也不受影响,但它对质料控制的要求稀奇高。

IMEC、麻省理工学院等机构都确立了自组装产线,研究它的详细工艺。基于DSA手艺,研究职员提出一种金属二硫化物晶体管自生长手艺,可将二维半导体晶体管尺寸缩小到现在的千分之一巨细,且功耗也只有现在的千分之一。

DSA 手艺于 1990 年月首次提出,并于 2007 年成为 ITRS 蹊径图的一部门。DSA 的主要支持者是 IMEC 的一个研究小组。2021 年,IMEC展示了使用 DSA 形成 18nm间距线图案。据领会,DSA光刻尚未被任何主要半导体代工厂用于大批量生产。在已往的二十年里,这项手艺举行了大量的研发和专利流动,但还没有商业用途。

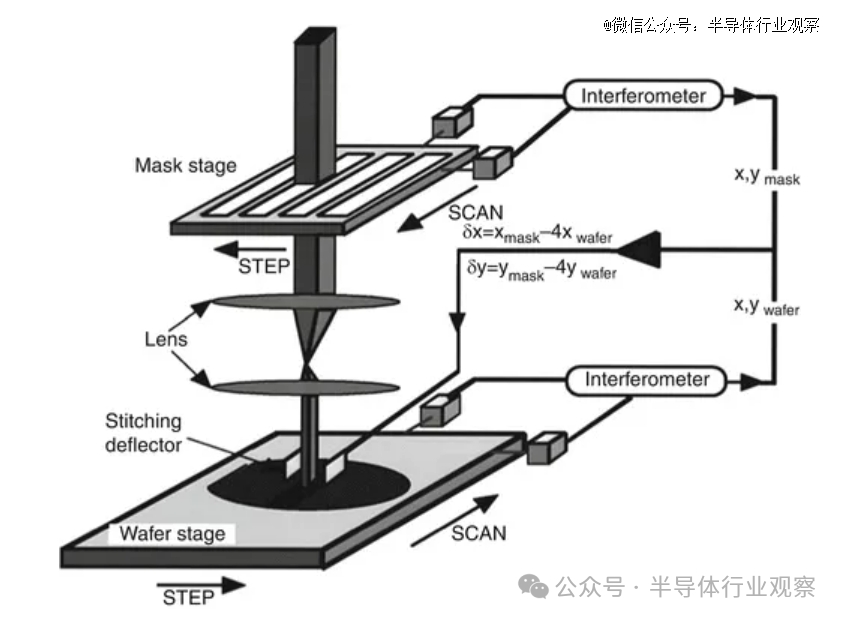

电子束光刻(EBL&MEBL)

电子束光刻(EBL)是一种行使高能电子束来替换光源,直接在硅片上镌刻图案的方式,它的分辨率相比于EUV光刻更高,但制造速率很慢,只能逐步描绘,不适合大规模量产。现在它主要用在量子盘算芯片、超外面芯片等高精度小批量芯片中。

电子束光刻原理图(图源:SpringerLink)

在此基础上,业界还推出了MB Platform——全球首创的多柱电子束光刻,该手艺将以新的生产力优势彻底改变了电子束光刻 (EBL),同时实现了高分辨率、细腻特征、宽视野和大景深。

现实上,早在20 世纪 80 年月,IBM就开发出了这种直写光刻手艺。从原理上看,多光束直写行使加速电子束在涂有电子束敏感光刻胶的基板上描绘出小于 10 纳米的特征。露出在电子束下会改变光刻胶的消融度,从而能够通过将光刻胶浸入显影剂中来选择性地去除光刻胶的露出或未露出区域。

由于不需要昂贵的光掩模,直写手艺很有吸引力。但单光束电子束光刻的吞吐量太慢,对于批量 IC 生产来说成本太高。剖析人士也直言,直写真正的问题是吞吐量。直接写入光刻手艺,纵然有数十万甚至一百万个光束,但对于晶圆光刻来说也太慢了。

因此,单光束直写工具只能用于复合半导体和光子学等小众应用。包罗KLA,Mapper在内的早期介入者,退出的退出,被收购的被收购。

Multibeam首席执行官兼董事长David K. Lam在接受采访时示意,希望依附MEBL手艺,中兴这项已有几十年历史的手艺。这就像拥有印刷机或3D打印机的速率,但又具有铅笔的定制天真性温顺应性,Multibeam可以使芯片制造的某些部门的生产效率比现有系统凌驾100倍。

X射线光刻手艺(XIL)

X射线的波长很短,险些没有衍射效应,早在二十世纪八十年月就进入了光刻手艺研发的视野内。

九十年月,IBM在美国佛蒙特州建了一条接纳同步辐射光源的X射线光刻机为主力的高频芯片生产线。昔时X射线光刻手艺,是那时的下一代光刻手艺的强有力竞争者。但随着准分子激光和氟化镓(GaF)透镜手艺的成熟,深紫外光(DUV)光刻手艺得以生长,在分辨率和经济性上优于X射线光刻。

近年来,俄罗斯重新提出使用X射线举行无掩膜的直接光刻,来制造7nm的芯片,目的是在2028年实现大规模量产。

X射线光刻原理图(图源:Advances)

写在最后

摩尔定律本质上是一个经济纪律。

在一个抽象的层面上,摩尔定律并不但单绑定某一个详细手艺。已往几十年,半导体公司把芯片产物分发到更大的市场,把产物的研发生产用度分摊到更大的基数上,以提高单品的利润率。然后,再把利润投入得手艺升级,晶体管小型化,性能提高,再进一步降低单品价钱,由于价钱降低又发现了更多更大的应用市场,云云不停良性循环。

若是从更久远的历史视角看,根据未来学家 Ray Kurzweil 的话说,摩尔定律只是几百年来,人类的盘算手艺——从算盘得手摇机械盘算机再到继电器、真空管、晶体管,进而到大规模集成电路的演变——在已往五十年的自然体现。

时至今日,随着芯片制程微缩靠近物理极限,EUV光刻装备价钱飞速飙升,摩尔定律的经济纪律正在被打破。

人们曾多次预言EUV光刻手艺将被其他手艺所替换。在以下的年份,甚至以为继任者已经准备停当:

1972年Spears和Smith提出的X射线光刻手艺(XRL);

1980年飞利浦公司开发的电子束图案天生器(EBPG);

1995年Chou提出的纳米压印光刻手艺(NIL);

2000年Kruit等人在Mapper公司开发的电子束并行写入手艺;

2010年提出的X射线过问光刻手艺(XIL)。

EUV光刻替换手艺的不停提高正推动半导体领域的快速提高。受到成本与效率的双重考量,以及近期半导体供应链平安问题的迫切压力,各国有十足动力开发EUV光刻的替换方案。

然而只管这些替换手艺均出现出伟大的潜力,但它们仍需深入的研究和改善,以解决手艺成熟度和商业化方面的挑战。这一历程将为半导体产业提供新的生长时机,推动手艺的不停演进与升级。